| MEMORIAS |  LEDS Y SENSORES DE TEMPERATURA |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

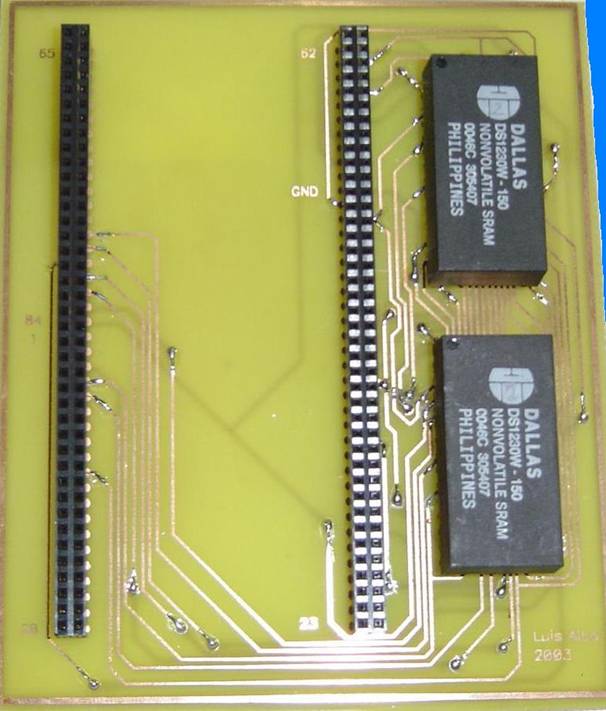

Esquema |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Memoria pin |

Memoria XS40 FPGA pin |

Memoria1 expansión FPGA pin |

Memoria2 expansión FPGA pin |

|

A0 |

3 |

3 |

3 |

|

A1 |

4 |

4 |

4 |

|

A2 |

5 |

5 |

5 |

|

A3 |

78 |

78 |

78 |

|

A4 |

79 |

79 |

79 |

|

A5 |

82 |

82 |

82 |

|

A6 |

83 |

83 |

83 |

|

A7 |

84 |

84 |

84 |

|

A8 |

59 |

59 |

59 |

|

A9 |

57 |

57 |

57 |

|

A10 |

51 |

51 |

51 |

|

A11 |

56 |

56 |

56 |

|

A12 |

50 |

50 |

50 |

|

A13 |

58 |

58 |

58 |

|

A14 |

60 |

60 |

60 |

|

D0 |

41 |

41 |

41 |

|

D1 |

40 |

40 |

40 |

|

D2 |

39 |

39 |

39 |

|

D3 |

38 |

38 |

38 |

|

D4 |

35 |

35 |

35 |

|

D5 |

81 |

81 |

81 |

|

D6 |

80 |

80 |

80 |

|

D7 |

10 |

10 |

10 |

|

/CE |

65 |

29 |

37 |

|

/OE |

61 |

61 |

61 |

|

/WE |

62 |

62 |

62 |

Fichero .ucf

NET ce1 LOC = P29;

NET ce2 LOC = P37;

NET we LOC = P62;

NET oe LOC = P61;

NET ramio<0> LOC = P41;

NET ramio<1> LOC = P40;

NET ramio<2> LOC = P39;

NET ramio<3> LOC = P38;

NET ramio<4> LOC = P35;

NET ramio<5> LOC = P81;

NET ramio<6> LOC = P80;

NET ramio<7> LOC = P10;

NET ramaddr<0> LOC = P3;

NET ramaddr<1> LOC = P4;

NET ramaddr<2> LOC = P5;

NET ramaddr<3> LOC = P78;

NET ramaddr<4> LOC = P79;

NET ramaddr<5> LOC = P82;

NET ramaddr<6> LOC = P83;

NET ramaddr<7> LOC = P84;

NET ramaddr<8> LOC = P59;

NET ramaddr<9> LOC = P57;

NET ramaddr<10> LOC = P51;

NET ramaddr<11> LOC = P56;

NET ramaddr<12> LOC = P50;

NET ramaddr<13> LOC = P58;

NET ramaddr<14> LOC = P60;

Catálogos

2.

LEDs Y SENSORES DE

TEMPERATURA

3. MEMORIAS